Product Summary

The EPF81500AGC280-4 is a Flexible Logic Element Matrix. It combines the benefits of both erasable programmable logic devices (EPLDs) and field-programmable gate arrays (FPGAs). The EPF81500AGC280-4 is ideal for a variety of applications because it combines the fine-grained architecture and high register count characteristics of FPGAs with the high speed and predictable interconnect delays of EPLDs. Logic is implemented in LEs that include compact 4-input look-up tables (LUTs) and programmable registers. The EPF81500AGC280-4 hashiigh performance which is provided by a fast, continuous network of routing resources.

Parametrics

EPF81500AGC280-4 absolute maximum ratings: (1)VCC, Supply voltage With respect to ground: –2.0 to 7.0 V; (2)VI, DC input voltage: –2.0 to 7.0 V; (3)IOUT, DC output current, per pin: –25 to 25 mA; (4)TSTG, Storage temperature No bias: –65 to 150 ℃; (5)TAMB, Ambient temperature Under bias: –65 to 135 ℃; (6)TJ, Junction temperature Ceramic packages, under bias: 150 ℃; (7)PQFP and RQFP, under bias: 135℃.

Features

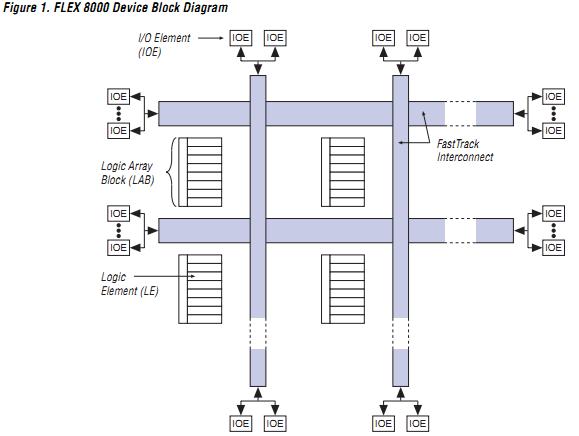

EPF81500AGC280-4 features: (1)In-circuit reconfigurability (ICR) via external Configuration EPROM or intelligent controller; (2)Fully compliant with the peripheral component interconnect (PCI) standard; (3)Built-in Joint-Test Action Group (JTAG) boundary-scan test (BST) circuitry compliant with IEEE Std. 1149.1-1990 on selected devices; (4)MultiVolt I/O interface enabling device core to run at 5.0 V, while I/O pins are compatible with 5.0-V and 3.3-V logic levels; (5)Low power consumption (typical specification less than 0.5 mA in standby mode); (6)FastTrack Interconnect continuous routing structure for fast, predictable interconnect delays; (7)Dedicated carry chain that implements arithmetic functions such as fast adders, counters, and comparators (automatically used by software tools and megafunctions); (8)Dedicated cascade chain that implements high-speed, high-fan-in logic functions (automatically used by software tools and megafunctions); (9)Tri-state emulation that implements internal tri-state nets Powerful I/O pins; (10)Programmable output slew-rate control reduces switching noise Peripheral register for fast setup and clock-to-output delay.

Diagrams

|

EPF81188AQC208-4 |

|

IC FLEX 8000A FPGA 12K 208-PQFP |

Data Sheet |

|

|

||||||

|

EPF81500AQC240-2 |

|

IC FLEX 8000A FPGA 16K 240-PQFP |

Data Sheet |

|

|

||||||

|

EPF81500AQC240-3 |

Other |

|

Data Sheet |

Negotiable |

|

||||||

|

EPF81500ARC240-3 |

Other |

|

Data Sheet |

Negotiable |

|

||||||

|

EPF8282ALC84-2 |

|

IC FLEX 8000A FPGA 2.5K 84-PLCC |

Data Sheet |

|

|

||||||

|

EPF8282ALC84-4 |

|

IC FLEX 8000A FPGA 2.5K 84-PLCC |

Data Sheet |

|

|

||||||

(China (Mainland))

(China (Mainland))